- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

SiGeおよびSi選択エッチング技術

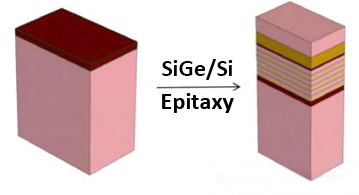

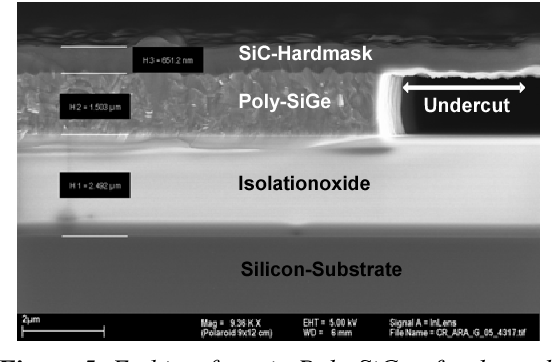

ゲートオールアラウンド FET (GAAFET) は、FinFET に代わる次世代トランジスタ アーキテクチャとして、より小さな寸法で優れた静電気制御と強化された性能を提供する能力で大きな注目を集めています。 n 型 GAAFET の製造における重要なステップには、高選択性が含まれます。エッチング内部スペーサーを堆積する前に、SiGe:Si スタックを形成し、シリコン ナノシートを生成し、チャネルを解放します。

この記事では、選択的なものについて詳しく説明します。エッチング技術は、このプロセスに関与しており、高酸化性ガスのプラズマフリー エッチングと原子層エッチング (ALE) という 2 つの新しいエッチング方法を導入し、SiGe エッチングで高精度と選択性を達成するための新しいソリューションを提供します。

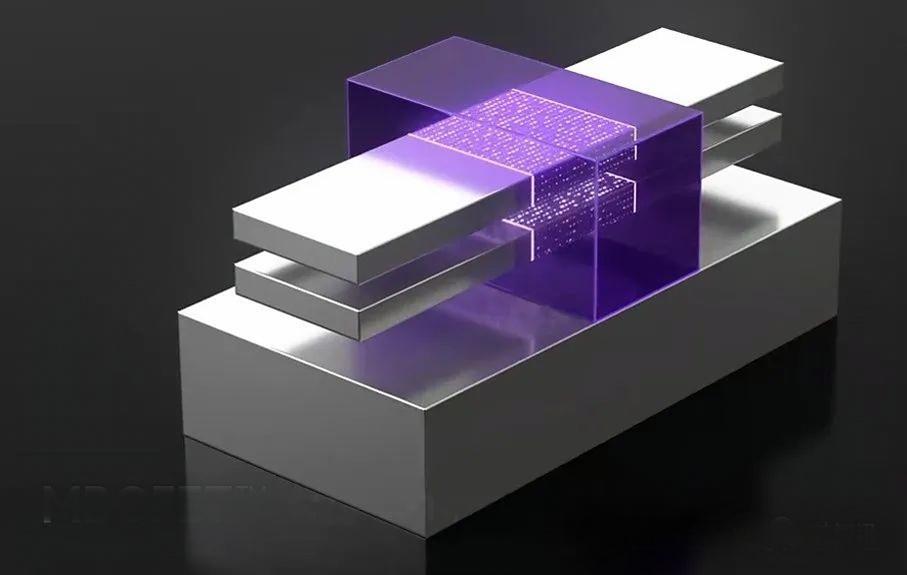

GAA 構造の SiGe 超格子層

GAAFET の設計では、デバイスの性能を向上させるために、Si と SiGe の交互層が使用されます。シリコン基板上にエピタキシャル成長させたもの、超格子として知られる多層構造を形成します。これらの SiGe 層はキャリア濃度を調整するだけでなく、応力を導入することで電子移動度を向上させます。ただし、後続のプロセスステップでは、シリコン層を保持したままこれらの SiGe 層を正確に除去する必要があり、選択性の高いエッチング技術が必要です。

SiGeの選択的エッチング方法

高酸化性ガスのプラズマフリー エッチング

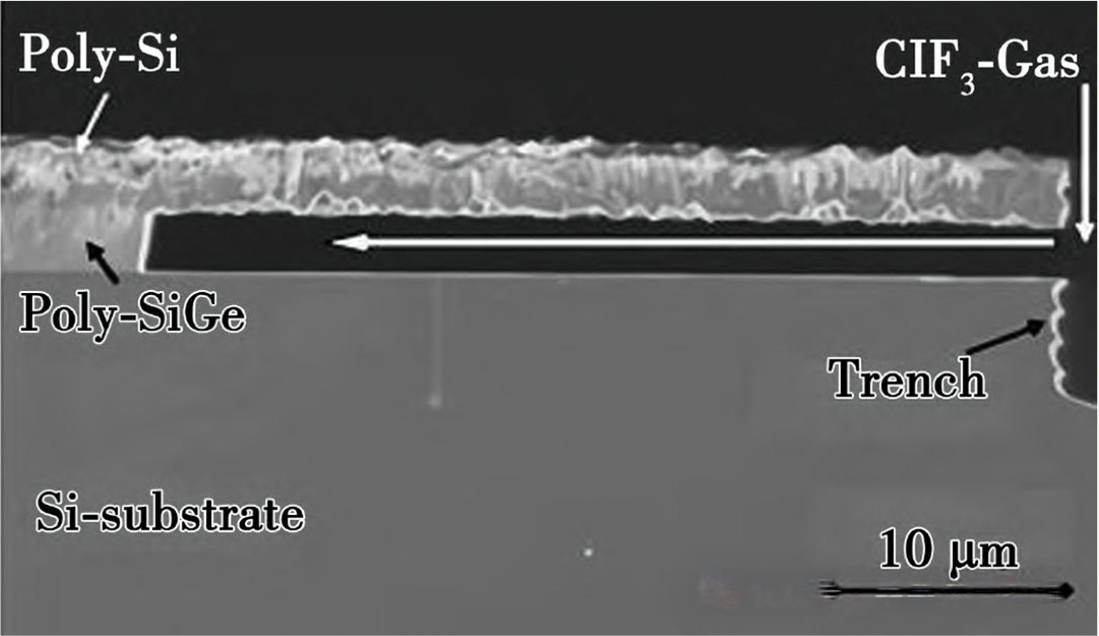

ClF3 ガスの選択: このエッチング方法では、ClF3 などの極端な選択性を備えた酸化性の高いガスが使用され、1000 ~ 5000 の SiGe:Si 選択比が達成されます。プラズマ損傷を引き起こすことなく室温で完了できます。

低温効率: 最適温度は約 30°C であり、低温条件下での高選択性エッチングを実現し、デバイスのパフォーマンスを維持するために重要な追加の熱バジェットの増加を回避します。

乾燥環境:全体エッチング工程完全に乾燥した状態で行われるため、構造物が接着するリスクが排除されます。

原子層エッチング (ALE)

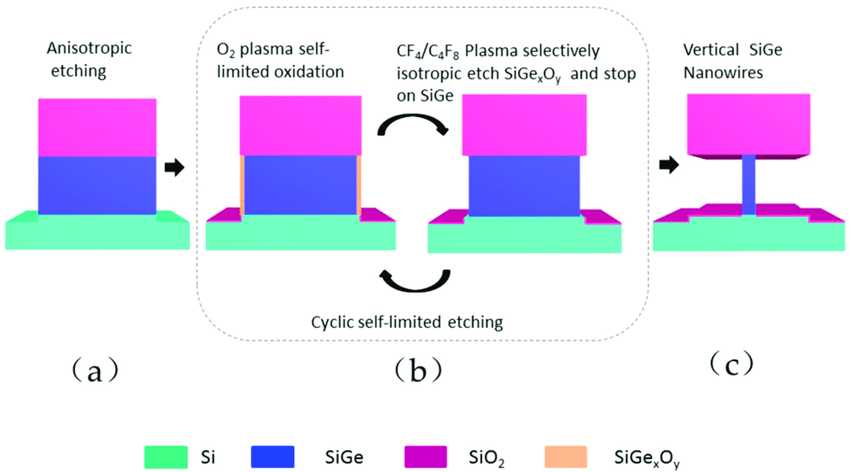

自己制限特性: ALE は 2 段階の循環ですエッチング技術ここでは、エッチングされる材料の表面が最初に改質され、次に未改質部分に影響を与えることなく改質層が除去されます。各ステップは自己制限的であり、一度にわずか数個の原子層を除去するレベルの精度を保証します。

サイクルエッチング: 所望のエッチング深さに達するまで、前述の 2 つのステップを繰り返します。このプロセスにより、ALE は次のことを実現します。原子レベルの精密エッチング内壁の小さな空洞にあります。

私たちセミコレックスは、SiC/TaC コーティングされたグラファイト ソリューション半導体製造のエッチング工程に応用されておりますので、ご不明な点や詳細が必要な場合はお気軽にお問い合わせください。

連絡先電話番号: +86-13567891907

電子メール: sales@semicorex.com