- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

チップ製造における SiGe: 専門ニュース レポート

半導体材料の進化

現代の半導体技術の分野では、微細化への絶え間ない取り組みにより、従来のシリコンベースの材料の限界が押し上げられています。高性能と低消費電力の要求を満たすために、SiGe (シリコン ゲルマニウム) は、その独特の物理的および電気的特性により、半導体チップ製造において最適な複合材料として浮上しています。この記事では、エピタキシープロセスSiGe の概要と、エピタキシャル成長、歪みシリコンの用途、およびゲートオールアラウンド (GAA) 構造におけるその役割について説明します。

SiGe エピタキシーの重要性

1.1 チップ製造におけるエピタキシーの概要:

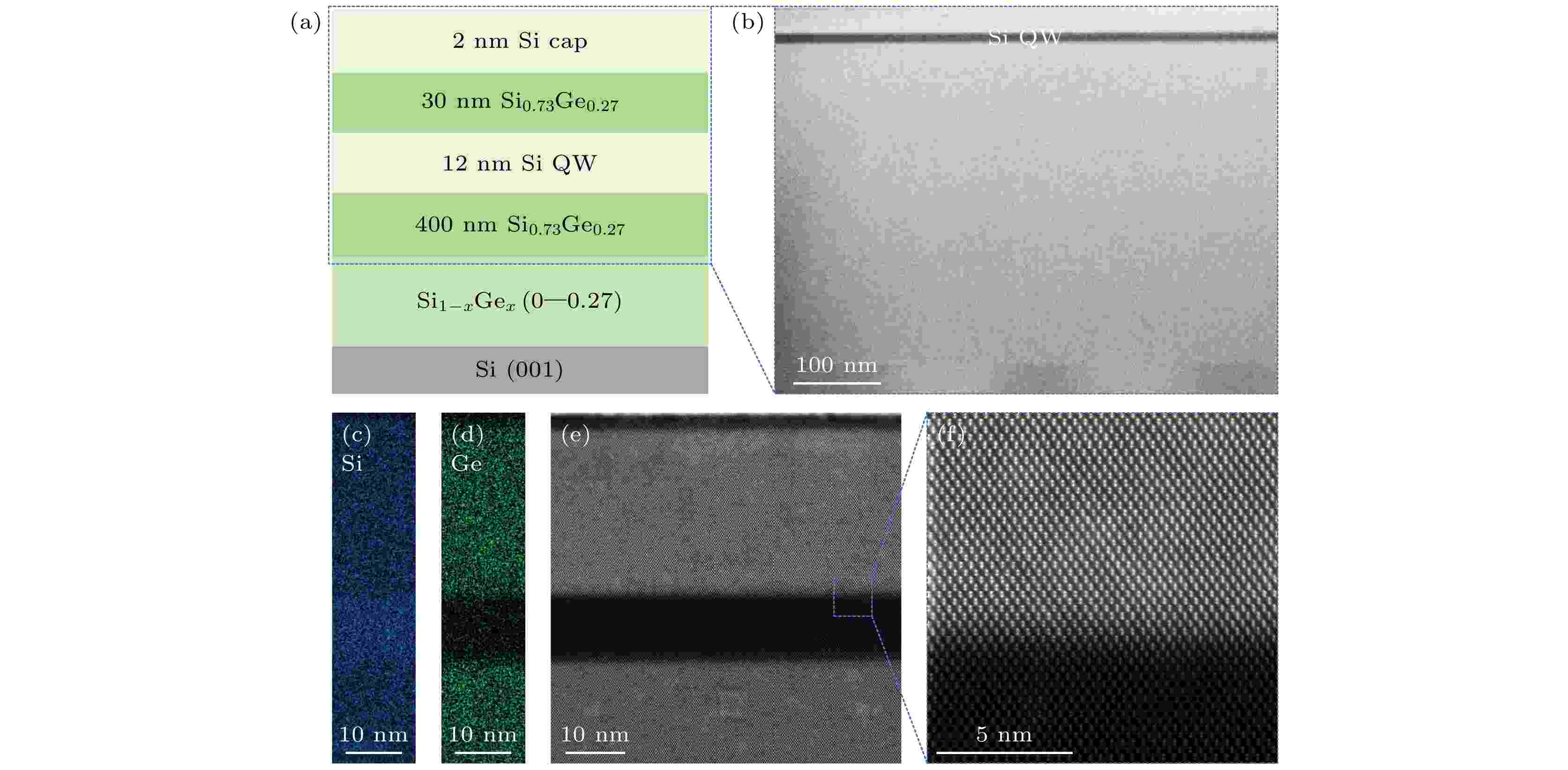

エピタキシーは、エピと略されることが多く、単結晶基板上に同じ格子配置で単結晶層を成長させることを指します。このレイヤーは次のいずれかになりますホモエピタキシャル(Si/Siなど)またはヘテロエピタキシャル (SiGe/Si または SiC/Si など)。エピタキシャル成長には、分子線エピタキシー (MBE)、超高真空化学蒸着 (UHV/CVD)、常圧および減圧エピタキシー (ATM および RP エピタキシー) などのさまざまな方法が使用されます。この記事では、シリコンを基板材料として半導体集積回路の製造に広く使用されているシリコン (Si) およびシリコンゲルマニウム (SiGe) のエピタキシープロセスに焦点を当てます。

1.2 SiGe エピタキシーの利点:

一定の割合のゲルマニウム(Ge)を導入することで、エピタキシープロセスバンドギャップ幅を縮小するだけでなく、トランジスタのカットオフ周波数 (fT) を増加させる SiGe 単結晶層を形成します。これにより、無線および光通信用の高周波デバイスに広く適用できます。さらに、高度な CMOS 集積回路プロセスでは、Ge と Si 間の格子不整合 (約 4%) により格子応力が生じ、電子または正孔の移動度が向上し、デバイスの飽和電流と応答速度が向上します。

包括的な SiGe エピタキシー プロセス フロー

2.1 前処理:

シリコンウェーハは、主にウェーハ表面の自然酸化層と不純物の除去を含む、望ましいプロセス結果に基づいて前処理されます。高濃度にドープされた基板ウェーハの場合、その後の工程での自動ドーピングを減らすためにバックシールが必要かどうかを検討することが重要です。エピタキシー成長.

2.2 成長ガスと条件:

シリコン ガス: シラン (SiH4)、ジクロロシラン (DCS、SiH2Cl2)、およびトリクロロシラン (TCS、SiHCl3) は、最も一般的に使用される 3 つのシリコン ガス ソースです。 SiH₄ は低温フルエピタキシープロセスに適していますが、成長速度が速いことで知られる TCS は厚いエピタキシープロセスの準備に広く使用されています。シリコンエピタキシー層。

ゲルマニウム ガス: ゲルマン (GeH₄) はゲルマニウムを添加するための主なソースであり、SiGe 合金を形成するためにシリコン ソースと組み合わせて使用されます。

選択的エピタキシー: 選択的成長は、エピタキシャル堆積塩素含有シリコンガス DCS を使用したその場エッチング。この選択性は、シリコン表面への Cl 原子の吸着が酸化物や窒化物よりも少ないためであり、エピタキシャル成長が容易になります。 SiH4 は Cl 原子が欠如しており、活性化エネルギーが低いため、一般に低温のフルエピタキシープロセスにのみ適用されます。もう 1 つの一般的に使用されるシリコン ソースである TCS は蒸気圧が低く、室温では液体であるため、反応チャンバーに導入するには H2 バブリングが必要です。ただし、比較的安価であり、成長速度が速い(最大 5 μm/分)ため、より厚いシリコン エピタキシー層を成長させるためによく使用され、シリコン エピタキシー ウェーハの製造に広く適用されています。

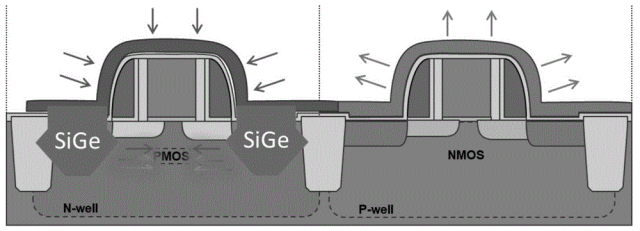

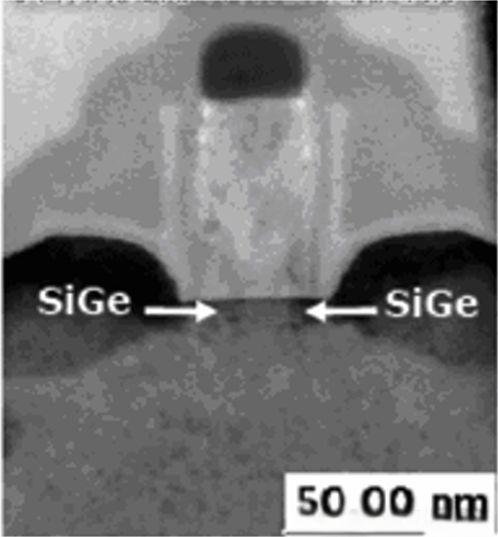

エピタキシャル層内の歪みシリコン

その間エピタキシャル成長では、エピタキシャル単結晶 Si が緩和 SiGe 層上に堆積されます。 Si と SiGe 間の格子不整合により、Si 単結晶層は下にある SiGe 層からの引張応力を受け、NMOS トランジスタの電子移動度が大幅に向上します。この技術は飽和電流 (Idsat) を増加させるだけでなく、デバイスの応答速度も向上します。 PMOS デバイスの場合、エッチング後にソース領域とドレイン領域に SiGe 層がエピタキシャル成長され、チャネルに圧縮応力が導入され、正孔移動度が向上し、飽和電流が増加します。

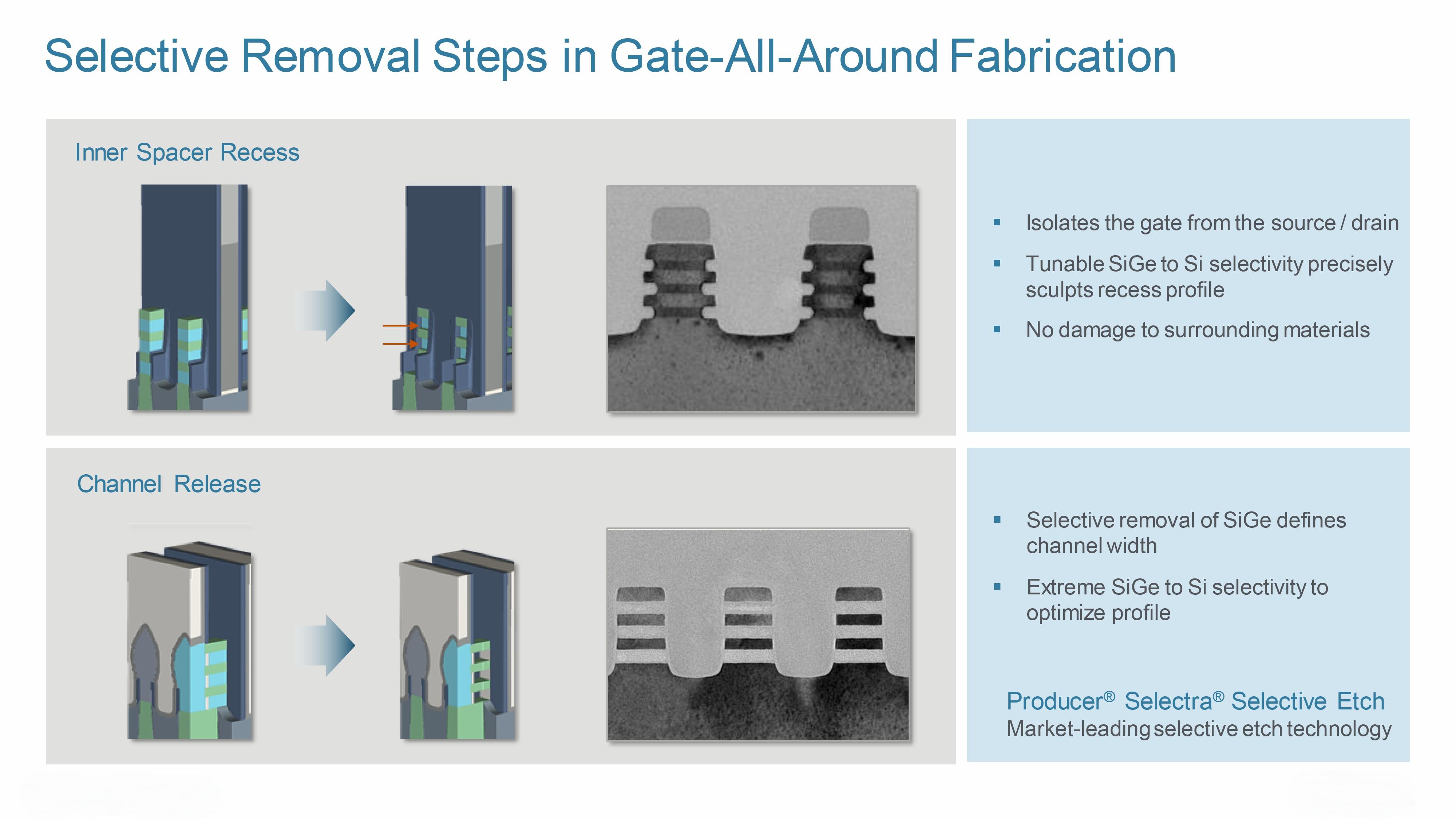

GAA 構造の犠牲層としての SiGe

ゲート オール アラウンド (GAA) ナノワイヤ トランジスタの製造では、SiGe 層が犠牲層として機能します。準原子層エッチング (準 ALE) などの高選択性異方性エッチング技術を使用すると、SiGe 層を正確に除去してナノワイヤまたはナノシート構造を形成できます。

私たちセミコレックスは、SiC/TaC コーティングされたグラファイト ソリューション半導体製造におけるSiエピタキシャル成長に応用されております。ご不明な点や詳細が必要な場合は、お気軽にお問い合わせください。

連絡先電話番号: +86-13567891907

電子メール: sales@semicorex.com