- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

チップ製造: 薄膜プロセス

薄膜プロセスの基礎入門とは何ですか?

半導体薄膜堆積プロセスは、現代のマイクロエレクトロニクス技術の重要な要素です。これには、半導体基板上に 1 つ以上の材料の薄い層を堆積することによって複雑な集積回路を構築することが含まれます。これらの薄膜は金属、絶縁体、または半導体材料であり、それぞれがチップのさまざまな層で導電、絶縁、保護などの異なる役割を果たします。これらの薄膜の品質は、チップの性能、信頼性、コストに直接影響します。したがって、薄膜堆積技術の開発は半導体産業にとって非常に重要です。

薄膜プロセスはどのように分類されますか?

現在、主流の薄膜成膜装置や技術には以下のようなものがあります。物理蒸着 (PVD)、化学蒸着 (CVD)、および原子層蒸着 (ALD)。これら 3 つの技術は、堆積原理、材料、適用可能な膜層、およびプロセスにおいて大きく異なります。

1. 物理蒸着 (PVD)

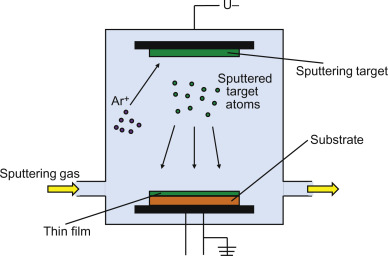

物理蒸着 (PVD) は純粋に物理的なプロセスであり、材料が蒸着またはスパッタリングによって気化され、基板上で凝縮されて薄膜が形成されます。

真空蒸着: 材料は高真空条件下で加熱されて蒸発し、基板上に蒸着されます。

スパッタリング: ガス放電によって生成されたガスイオンがターゲット材料に高速で衝突し、基板上に膜を形成する原子を除去します。

イオンプレーティング: 真空蒸着とスパッタリングの利点を組み合わせたもので、蒸発した材料が放電空間内で部分的にイオン化され、基板に引き寄せられて膜が形成されます。

特徴: PVD は化学反応を行わず、物理的変化のみを伴います。

2. 化学蒸着 (CVD)

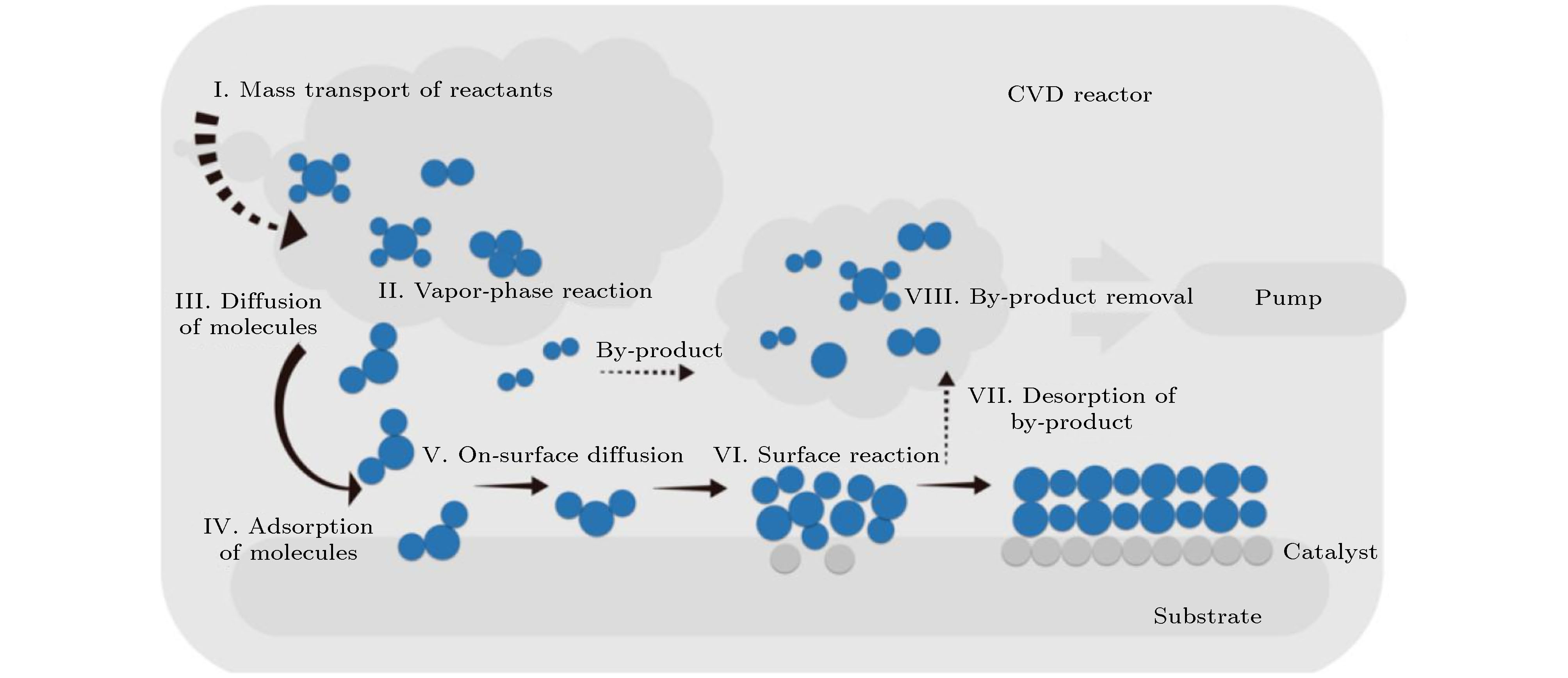

化学蒸着 (CVD) は、気相化学反応を利用して基板上に固体薄膜を形成する技術です。

従来の CVD: さまざまな誘電体および半導体膜の堆積に適しています。

プラズマ強化 CVD (PECVD): プラズマを使用して反応活性を高め、低温成膜に適しています。

高密度プラズマ CVD (HDPCVD): 堆積とエッチングを同時に行うことができ、優れた高アスペクト比のギャップ充填機能を提供します。

減圧 CVD (SACVD): 高温で生成される高活性酸素ラジカルを使用することにより、高圧条件下で優れたホール充填能力を実現します。

有機金属 CVD (MOCVD): GaN などの半導体材料に適しています。

特徴: CVD にはシラン、ホスフィン、ボラン、アンモニア、酸素などの気相反応物質が含まれ、高温、高圧、またはプラズマ条件下で窒化物、酸化物、酸窒化物、炭化物、ポリシリコンなどの固体膜を生成します。

3. 原子層堆積(ALD)

原子層堆積 (ALD) は、2 つ以上の反応物質を交互にパルス導入する特殊な CVD 技術で、正確な単一原子層堆積を実現します。

熱 ALD (TALD): 基板上での前駆体の吸着とその後の化学反応に熱エネルギーを使用します。

プラズマ強化 ALD (PEALD): プラズマを使用して反応活性を強化し、低温でのより速い成膜速度を可能にします。

特徴: ALD は正確な膜厚制御、優れた均一性、一貫性を備えているため、深いトレンチ構造での膜成長に非常に適しています。

さまざまな薄膜プロセスはチップにどのように適用されますか?

金属層: PVD は主に、アルミニウム パッド、金属ハード マスク、銅バリア層、銅シード層などの超高純度金属および遷移金属窒化物膜を堆積するために使用されます。

Alパッド:PCB用ボンディングパッド。

メタルハードマスク: 通常、フォトリソグラフィーで使用される TiN。

Cu バリア層: 通常は TaN であり、Cu の拡散を防ぎます。

Cu シード層: 純粋な Cu または Cu 合金。後続の電気めっきのシード層として使用されます。

誘電体層: CVD は主に、窒化物、酸化物、酸窒化物、炭化物、ポリシリコンなどのさまざまな絶縁材料を堆積するために使用され、さまざまな回路コンポーネントを分離し、干渉を低減します。

ゲート酸化層: ゲートとチャネルを分離します。

層間絶縁膜: 異なる金属層を分離します。

バリア層: PVD は、金属の拡散を防止し、デバイスを汚染から保護するために使用されます。

Cu バリア層: 銅の拡散を防ぎ、デバイスのパフォーマンスを確保します。

ハードマスク: PVD は、デバイス構造の定義を支援するためにフォトリソグラフィーで使用されます。

メタル ハード マスク: 通常は TiN、パターンを定義するために使用されます。

自己整合ダブルパターニング (SADP): ALD は、FinFET のフィン構造の製造に適した、より微細なパターニングにスペーサー層を使用します。

FinFET: スペーサー層を使用してコア パターンのエッジにハード マスクを作成し、空間周波数の乗算を実現します。

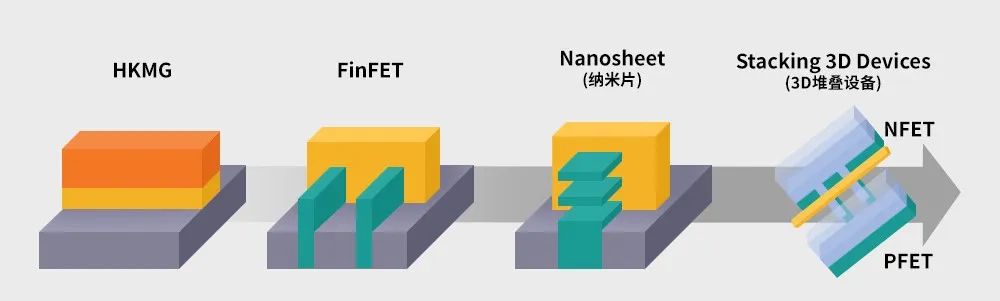

High-K メタル ゲート (HKMG): ALD は、高誘電率材料とメタル ゲートの堆積に使用され、特に 28nm 以下のプロセスでトランジスタの性能を向上させます。

High-K 誘電体層: HfO2 が最も一般的な選択であり、ALD が好ましい作製方法です。

メタルゲート: Hf 要素とポリシリコンゲートの非互換性のために開発されました。

その他のアプリケーション: ALD は、銅配線の拡散バリア層やその他の技術でも広く使用されています。

銅相互接続拡散バリア層: 銅の拡散を防止し、デバイスのパフォーマンスを保護します。

上記の紹介から、PVD、CVD、および ALD には独自の特性と利点があり、半導体製造においてかけがえのない役割を果たしていることがわかります。 PVD は主に金属膜の堆積に使用され、CVD はさまざまな誘電体および半導体膜の堆積に適していますが、ALD は優れた厚さ制御とステップ カバレージ機能により高度なプロセスに優れています。これらのテクノロジーの継続的な開発と改良は、半導体産業の進歩のための強固な基盤を提供します。**

私たちセミコレックスは、CVD SiC/TaC コーティング部品半導体製造に応用されておりますので、ご不明な点や詳細が必要な場合はお気軽にお問い合わせください。

連絡先電話番号: +86-13567891907

電子メール: sales@semicorex.com