- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

エピタキシャルウェーハプロセスとは

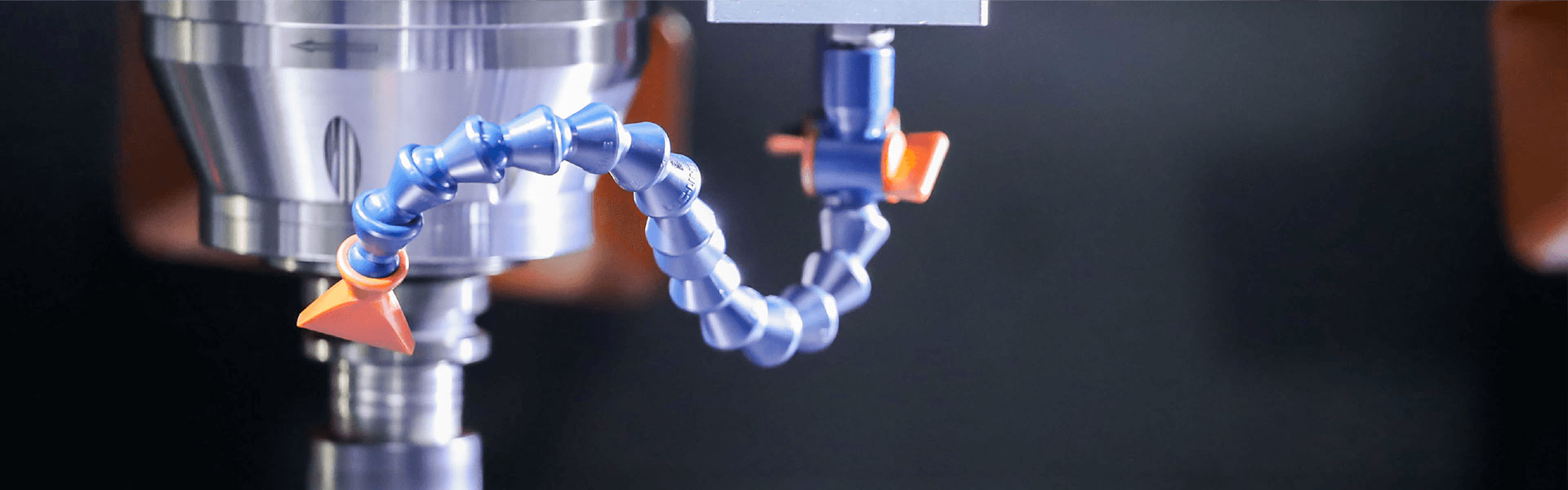

エピタキシャルウェーハプロセスは、半導体製造で使用される重要な技術です。これは、基板と同じ結晶構造と配向を持つ基板の上に結晶材料の薄層を成長させることを含みます。このプロセスにより、2 つの材料間に高品質のインターフェースが作成され、高度な電子デバイスの開発が可能になります。

エピタキシャルウェーハプロセスは、ダイオード、トランジスタ、集積回路など、さまざまな半導体デバイスの製造に使用されます。このプロセスは、通常、化学気相堆積(CVD)または分子線エピタキシー(MBE)技術を使用して実行されます。これらの技術は、基板表面への材料原子の堆積を含み、そこで結晶層を形成します。

エピタキシャルウェーハプロセスは、温度、圧力、ガス流量などのさまざまなパラメータを厳密に制御する必要がある複雑で精密な技術です。欠陥密度の低い高品質の結晶構造を確実に形成するには、エピタキシャル層の成長を注意深く制御する必要があります。

エピタキシャルウェーハプロセスの品質は、結果として得られる半導体デバイスの性能にとって重要です。エピタキシャル層は、最適な電子特性を確保するために、均一な厚さ、低い欠陥密度、および高レベルの純度を備えている必要があります。エピタキシャル層の厚さとドーピングレベルを正確に制御して、導電率やバンドギャップなどの所望の特性を実現できます。

近年、高性能半導体デバイス、特にパワーエレクトロニクスの分野において、エピタキシャルウェーハプロセスの重要性が増しています。効率と信頼性が向上した高性能デバイスに対する需要は、高度なエピタキシャルウェーハプロセスの開発を推進しています。

エピタキシャルウェーハプロセスは、温度センサー、ガスセンサー、圧力センサーなどの高度なセンサーの開発にも使用されています。これらのセンサーには、特定の電子特性を備えた高品質の結晶層が必要ですが、これはエピタキシャル ウェーハ プロセスによって実現できます。