- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

3C-SiC のヘテロエピタキシー: 概要

1. 3C-SiCの歴史的発展

炭化ケイ素の重要なポリタイプである 3C-SiC の開発は、半導体材料科学の継続的な進歩を反映しています。 1980年代、西野らは、は、化学蒸着 (CVD) を使用してシリコン基板上に厚さ 4 μm の 3C-SiC 膜を初めて達成し[1]、3C-SiC 薄膜技術の基礎を築きました。

1990 年代は SiC 研究の黄金時代を迎えました。 Cree Research Inc. がそれぞれ 1991 年と 1994 年に 6H-SiC チップと 4H-SiC チップを発売したことにより、SiC 半導体デバイスの商品化が推進されました。この技術の進歩は、その後の 3C-SiC の研究と応用の基礎を築きました。

21 世紀初頭、中国でもシリコンベースの SiC フィルムが大きな進歩を遂げました。 Ye Zhizhenら。 An Xiaらは2002年に低温でCVDを使用してシリコン基板上にSiC膜を作製した[2]。 2001 年に室温でマグネトロン スパッタリングを使用して同様の結果を達成しました[3]。

しかし、Si と SiC 間の大きな格子不整合 (約 20%) により、3C-SiC エピタキシャル層の欠陥密度、特に二重位置境界 (DPB) が高くなりました。これを軽減するために、研究者らは 3C-SiC エピタキシャル層の成長に (0001) 配向の 6H-SiC、15R-SiC、または 4H-SiC などの基板を選択し、それによって欠陥密度を低減しました。たとえば、2012 年に関一明らは、は、過飽和を制御することによって 6H-SiC(0001) シード上で 3C-SiC および 6H-SiC の選択的成長を達成する、速度論的多形性制御技術を提案しました [4-5]。 2023 年に、Xun Li らはは、14 μm/h の速度で最適化された CVD 成長を使用して、4H-SiC 基板上に DPB のない滑らかな 3C-SiC エピタキシャル層を得ることに成功しました[6]。

2. 3C-SiCの結晶構造と応用

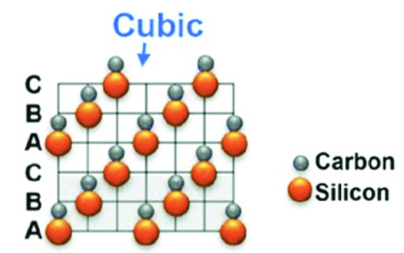

数多くの SiC ポリタイプの中で、β-SiC としても知られる 3C-SiC は唯一の立方体ポリタイプです。この結晶構造では、Si 原子と C 原子が 1 対 1 の比率で存在し、強い共有結合を持った四面体の単位胞を形成しています。この構造は、ABC-ABC-... の順序で配置された Si-C 二重層によって特徴付けられ、各単位セルには C3 表記で示される 3 つのそのような二重層が含まれています。図 1 に 3C-SiC の結晶構造を示します。

図 1. 3C-SiC の結晶構造

現在、パワーデバイスに最も広く使用されている半導体材料はシリコン(Si)です。ただし、その固有の制限によりパフォーマンスが制限されます。 4H-SiC や 6H-SiC と比較して、3C-SiC は室温で最も高い理論的電子移動度 (1000 cm2・V-1・s-1) を有しており、MOSFET アプリケーションにとってより有利です。さらに、3C-SiC は、高い絶縁破壊電圧、優れた熱伝導率、高硬度、広いバンドギャップ、高温耐性、および耐放射線性により、エレクトロニクス、オプトエレクトロニクス、センサー、および極限環境での用途に非常に有望です。

高出力、高周波、および高温のアプリケーション: 3C-SiC の高い降伏電圧と高い電子移動度は、特に要求の厳しい環境での MOSFET などのパワー デバイスの製造に最適です [7]。

ナノエレクトロニクスおよび微小電気機械システム (MEMS): シリコン技術との互換性により、ナノスケール構造の製造が可能になり、ナノエレクトロニクスや MEMS デバイスへの応用が可能になります [8]。

オプトエレクトロニクス:ワイドバンドギャップ半導体材料として、3C-SiC は青色発光ダイオード (LED) に適しています。その高い発光効率とドーピングの容易さにより、照明、ディスプレイ技術、レーザーの用途にとって魅力的となっています[9]。

センサー:3C-SiC は、位置感応型検出器、特に横方向光起電力効果に基づくレーザースポット位置感応型検出器に使用されます。これらの検出器はゼロバイアス条件下で高い感度を示すため、高精度位置決めアプリケーションに適しています[10]。

3. 3C-SiCヘテロエピタキシーの作製方法

3C-SiC ヘテロエピタキシーの一般的な方法には、化学蒸着 (CVD)、昇華エピタキシー (SE)、液相エピタキシー (LPE)、分子線エピタキシー (MBE)、およびマグネトロン スパッタリングが含まれます。 CVD は、温度、ガス流量、チャンバー圧力、反応時間の制御性と適応性により、エピタキシャル層の品質の最適化を可能にするため、3C-SiC エピタキシーに推奨される方法です。

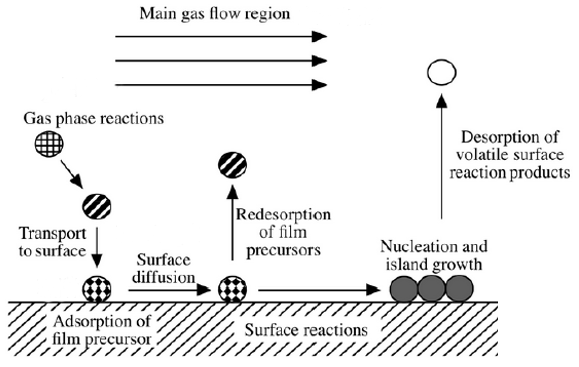

化学蒸着 (CVD):Si と C を含むガス状化合物は反応チャンバーに導入され、高温に加熱されて分解が起こります。その後、Si 原子と C 原子は、通常は Si、6H-SiC、15R-SiC、または 4H-SiC などの基板上に堆積します [11]。この反応は通常、1300 ~ 1500 ℃ の間で発生します。一般的な Si ソースには SiH4、TCS、および MTS が含まれますが、C ソースは主に C2H4 および C3H8 であり、キャリア ガスとして H2 が使用されます。図 2 は、CVD プロセスの概略図を示しています[12]。

図 2. CVD プロセスの概略図

昇華エピタキシー (SE):この方法では、6H-SiC または 4H-SiC 基板をるつぼの上部に置き、底部には原材料として高純度の SiC 粉末を置きます。るつぼは高周波誘導によって 1900 ~ 2100°C に加熱され、基板温度をソース温度よりも低く維持して軸方向の温度勾配を作成します。これにより、昇華した SiC が基板上で凝縮して結晶化し、3C-SiC ヘテロエピタキシーが形成されます。

分子線エピタキシー (MBE):この高度な薄膜成長技術は、4H-SiC または 6H-SiC 基板上に 3C-SiC エピタキシャル層を成長させるのに適しています。超高真空下では、原料ガスを精密に制御することで、構成元素の指向性のある原子線や分子線を形成することができます。これらのビームは、エピタキシャル成長のために加熱された基板表面に向けられます。

4. 結論と展望

継続的な技術進歩と詳細な機構研究により、3C-SiC ヘテロエピタキシーは半導体産業においてますます重要な役割を果たし、エネルギー効率の高い電子デバイスの開発を推進する態勢が整っています。低い欠陥密度を維持しながら成長速度を高めるための HCl 雰囲気の導入など、新しい成長技術の探求は、将来の研究にとって有望な手段です。欠陥形成メカニズムのさらなる研究と高度な特性評価技術の開発により、正確な欠陥制御と最適化された材料特性が可能になります。高品質で厚い 3C-SiC 膜の迅速な成長は、高電圧デバイスの要求を満たすために重要であり、成長速度と材料の均一性のバランスに対処するためにさらなる研究が必要です。 SiC/GaN などのヘテロ構造における 3C-SiC のアプリケーションを活用することで、パワーエレクトロニクス、光電子集積、量子情報処理などの新しいデバイスにおけるその可能性を最大限に探ることができます。

参考文献:

[1] 西野 伸、葉月 裕、松浪 宏 他スパッタリングされた SiC 中間層を備えたシリコン基板上の単結晶 β-SiC 膜の化学蒸着[J]。Journal of The Electrochemical Society、1980、127(12):2674-2680。

[2] Ye Zhizhen、Wang Yadong、Huang Jingyun、他、シリコンベースの炭化ケイ素薄膜の低温成長に関する研究 [J]、Journal of Vacuum Science and Technology、2002、022(001):58-60。 。

[3] An Xia、Zhuang Huizhao、Li Huaixiang、他、(111) Si 基板上でのマグネトロン スパッタリングによるナノ SiC 薄膜の作製 [J] 山東師範大学ジャーナル: 自然科学版、2001: 382-384。 ..

[4] 関 和人、アレキサンダー、小沢 伸、他。溶液成長における過飽和制御による SiC のポリタイプ選択的成長[J]。結晶成長ジャーナル、2012、360:176-180。

[5] Chen Yao、Zhao Fuqiang、Zhu Bingxian、He Shuai、国内外の炭化ケイ素パワーデバイスの開発の概要 [J]、2020: 49-54。

[6] Li X 、Wang G .形態が改善された 4H-SiC 基板上の 3C-SiC 層の CVD 成長[J].Solid State Communications、2023:371。

[7] Hou Kaiwen、Si パターン基板と 3C-SiC 成長への応用に関する研究 [D]、西安理工大学、2018 年。

[8]ラース、ヒラー、トーマスら。 3C-SiC(100) メサ構造の ECR エッチングにおける水素の影響[J]。マテリアル サイエンス フォーラム、2014。

[9] Xu Qingfang、レーザー化学蒸着による 3C-SiC 薄膜の作製、武漢理工大学、2016 年。

[10] Foisal AR M 、 Nguyen T 、 Dinh T K ら、3C-SiC/Si ヘテロ構造: 光起電力効果に基づく位置敏感検出器のための優れたプラットフォーム [J].ACS Applied Materials & Interfaces、2019: 40980-40987。

[11] Xin Bin. CVD プロセスに基づく 3C/4H-SiC ヘテロエピタキシャル成長: 欠陥の特性評価と進化 [D] 西安電子科学技術大学。

[12] Dong Lin、炭化ケイ素の大面積マルチウェーハエピタキシャル成長技術と物理的特性の特性評価、中国科学院大学、2014 年。

[13] ディアニ M 、サイモン L 、キューブラー L ら。 6H-SiC(0001)基板上での3C-SiCポリタイプの結晶成長[J]。結晶成長ジャーナル、2002、235(1):95-102。