- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

エピタキシャル層: 先端半導体デバイスの基礎

図 1: ユニポーラ デバイスのドーピング濃度、層の厚さ、およびブレークダウン電圧の間の相関関係を示します。

SiC エピタキシャル層の作製には、主に蒸着成長、液相エピタキシー (LPE)、分子線エピタキシー (MBE)、化学蒸着 (CVD) などの技術が含まれますが、工場での大量生産では CVD が主流の方法です。

表 1: 主なエピタキシャル層作製方法の比較概要を示します。

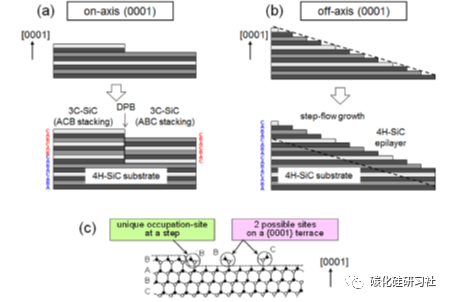

画期的なアプローチには、図 2(b) に示すように、特定の傾斜角でオフアクシス {0001} 基板上に成長することが含まれます。この方法では、ステップ サイズを縮小しながらステップ密度が大幅に増加し、主にステップ バンチング サイトでの核生成が促進されるため、エピタキシャル層が基板の積層順序を完全に複製できるようになり、ポリタイプの共存が排除されます。

図 2: 4H-SiC のステップ制御エピタキシーの物理プロセスを示します。

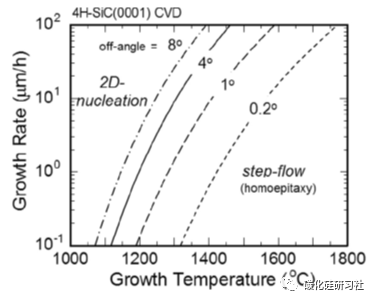

図 3: 4H-SiC のステップ制御エピタキシーにおける CVD 成長の臨界条件を示します。

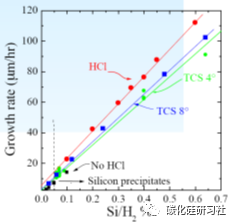

図 4: 4H-SiC エピタキシーのさまざまなシリコン ソースでの成長速度を比較します。

低電圧および中電圧アプリケーション (1200V デバイスなど) の領域では、SiC エピタキシー技術が成熟段階に達し、厚さ、ドーピング濃度、欠陥分布の均一性が比較的優れており、低電圧および中電圧 SBD の要件を適切に満たしています。 、MOS、JBS デバイスなど。

しかし、高電圧領域には依然として大きな課題があります。たとえば、定格 10000V のデバイスには厚さ約 100μm のエピタキシャル層が必要ですが、これらの層は、低電圧の対応物と比較して厚さとドーピングの均一性が大幅に劣っており、デバイス全体の性能に対する三角形の欠陥の悪影響は言うまでもありません。バイポーラデバイスに有利な傾向にある高電圧アプリケーションでは、少数キャリアの寿命にも厳しい要求が課されるため、このパラメータを向上させるためにプロセスの最適化が必要になります。

現在、市場は4インチと6インチのSiCエピタキシャルウェーハが主流であり、大口径SiCエピタキシャルウェーハの割合が徐々に増加している。 SiCエピタキシャルウェーハのサイズは基本的にSiC基板の寸法によって決まります。現在では 6 インチの SiC 基板が市販されており、4 インチから 6 インチの SiC エピタキシーへの移行は着実に進んでいます。

SiC 基板の製造技術が進歩し、生産能力が拡大するにつれて、SiC 基板のコストは徐々に低下しています。基板がエピタキシャルウェーハのコストの50%以上を占めることを考えると、基板価格の低下はSiCエピタキシャルのコスト低下につながり、それによって業界の明るい未来が約束されると予想されます。**